## LOGY 2.5A Monolithic Active Cell Balancer with Telemetry Interface

## **FEATURES**

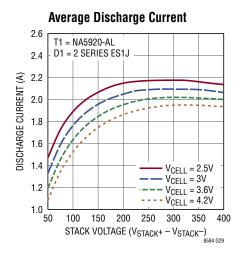

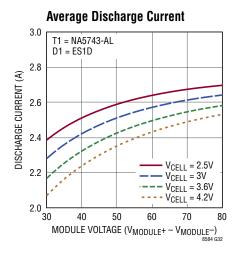

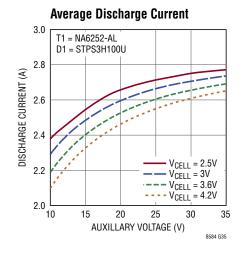

- 2.5A Typical Average Cell Discharge Current

- Integrated 6A, 50V Power Switch

- Integrates Seamlessly with LTC680x Family: No Additional Software Required

- Selectable Current and Temperature Monitors

- Ultralow Quiescent Current in Shutdown

- Engineered for ISO 26262 Compliant Systems

- Isolated Balancing:

- Can Return Charge to Top of Stack

- Can Return Charge to Any Combination of Cells in Stack

- Can Return Charge to 12V Battery for Alternator Replacement

- Can Be Paralleled for Greater Discharge Capability

- All Quiescent Current in Operation Taken from Local Cell

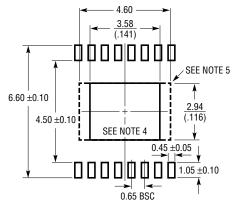

- 16-Lead TSSOP Package

## **APPLICATIONS**

- Active Battery Stack Balancing

- Electric and Hybrid Electric Vehicles

- Fail-Safe Power Supplies

- Energy Storage Systems

## DESCRIPTION

The LT®8584 is a monolithic flyback DC/DC converter designed to actively balance high voltage stacks of batteries. The high efficiency of a switching regulator significantly increases the achievable balancing current while reducing heat generation. Active balancing also allows for capacity recovery in stacks of mismatched batteries, a feat unattainable with passive balance systems. In a typical system, greater than 99% of the total battery capacity can be recovered.

The LT8584 includes an integrated 6A, 50V power switch, reducing the design complexity of the application circuit. The part runs completely off of the cell which it is discharging, removing the need for complicated biasing schemes commonly required for external power switches. The enable pin  $(D_{IN})$  of the part is designed to work seamlessly with the LTC680x family of battery stack voltage monitoring ICs. The LT8584 also provides system telemetry including current and temperature monitoring when used with the LTC680x family of parts. When the LT8584 is disabled, less than 20nA of total quiescent current is typically consumed from the battery.

(T, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and Hot Swap and isoSPI are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents, including 6518733 and 6636021.

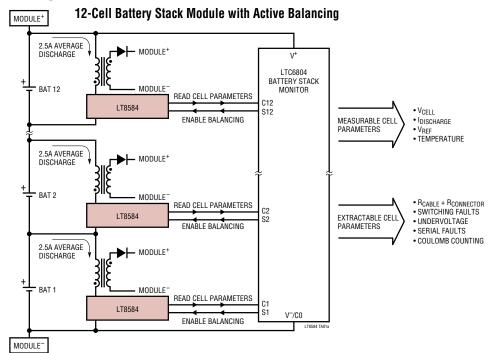

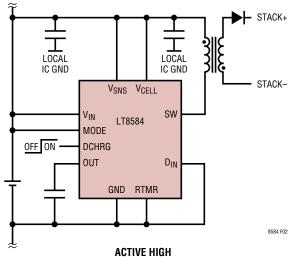

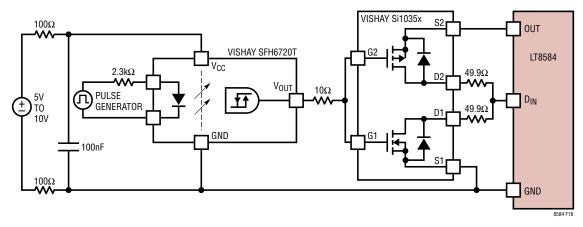

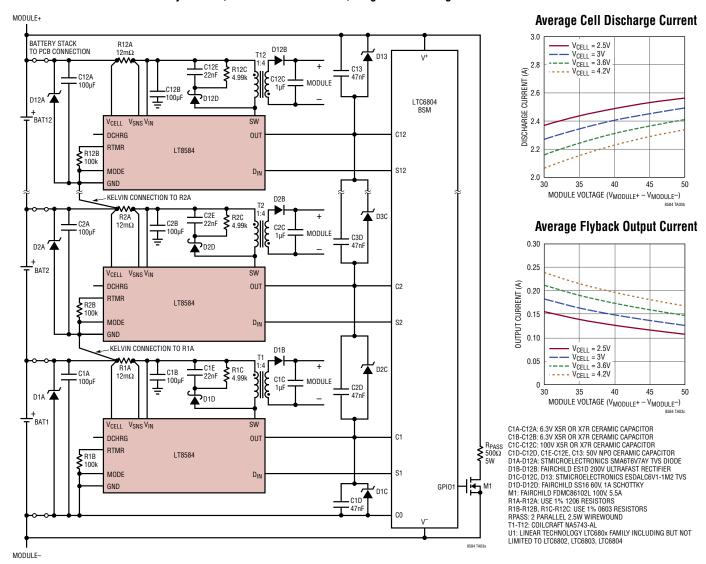

## TYPICAL APPLICATION

LINEAR

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| D <sub>IN</sub> to GND Voltage                                    | ±10V                                  |

|-------------------------------------------------------------------|---------------------------------------|

| V <sub>IN</sub> , V <sub>CELL</sub> , V <sub>SNS</sub> MODE, OUT, |                                       |

| DCHRG Voltage                                                     | 0.3V to 9V                            |

| RTMR Voltage                                                      |                                       |

| SW Voltage (Note 3)                                               | · · · · · · · · · · · · · · · · · · · |

| V <sub>IN</sub> – V <sub>CELL</sub> Voltage                       |                                       |

| V <sub>IN</sub> – V <sub>SNS</sub> Voltage                        |                                       |

| MODE – V <sub>IN</sub> Voltage                                    |                                       |

| V <sub>SNS</sub> , MODE Pin Current                               |                                       |

| V <sub>CELL</sub> , OUT Pin Current                               | ±10mA                                 |

| SW Pin Negative Current                                           | –2A                                   |

| Operating Junction Temperature Range                              | (Note 4)                              |

| LT8584E                                                           |                                       |

| LT8584I                                                           | 40°C to 125°C                         |

| LT8584H                                                           |                                       |

| Storage Temperature Range                                         | 65°C to 150°C                         |

| Lead Temperature (Soldering, 10 sec)                              | 300°C                                 |

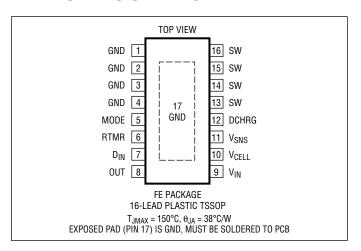

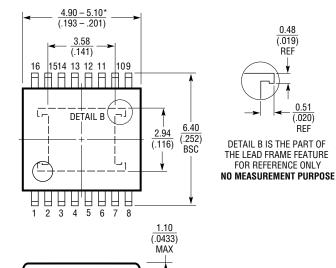

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL   | PART MARKING* | PACKAGE DESCRIPTION   | TEMPERATURE RANGE |

|------------------|-----------------|---------------|-----------------------|-------------------|

| LT8584EFE#PBF    | LT8584EFE#TRPBF | 8584FE        | 16-Lead Plastic TSSOP | -40°C to 125°C    |

| LT8584IFE#PBF    | LT8584IFE#TRPBF | 8584FE        | 16-Lead Plastic TSSOP | -40°C to 125°C    |

| LT8584HFE#PBF    | LT8584HFE#TRPBF | 8584FE        | 16-Lead Plastic TSSOP | -40°C to 150°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ . $V_{IN} = 4.2\text{V}$ , $D_{IN} = \text{GND}$ unless otherwise noted. (Note 4)

| PARAMETER                                        | CONDITIONS                                                                                                                                                                                                                |   | MIN                                           | TYP            | MAX                                    | UNITS                            |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------|----------------|----------------------------------------|----------------------------------|

| V <sub>IN</sub> Recommended Voltage Range        | Switching<br>Nonswitching                                                                                                                                                                                                 | • | 2.5<br>2.45                                   |                | 5.3<br>5.3                             | V                                |

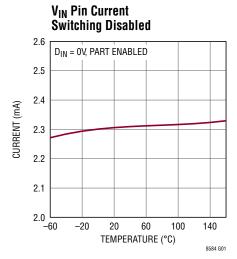

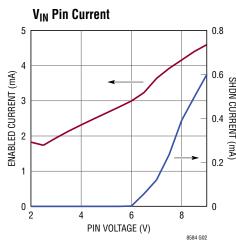

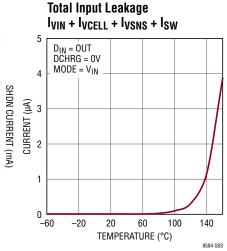

| V <sub>IN</sub> Quiescent Current                | Switching Nonswitching In Shutdown, D <sub>IN</sub> = OUT In Shutdown, D <sub>IN</sub> = OUT                                                                                                                              | • |                                               | 45<br>2.5<br>1 | 3<br>90<br>1                           | mA<br>mA<br>nA<br>μΑ             |

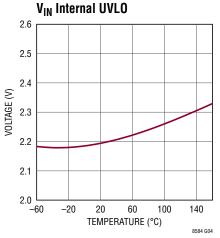

| V <sub>IN</sub> UVLO                             |                                                                                                                                                                                                                           | • | 2.1                                           |                | 2.45                                   | V                                |

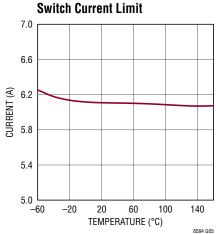

| Switch DC Current Limit                          |                                                                                                                                                                                                                           | • | 6                                             | 6.3            | 6.8                                    | А                                |

| Current Limit Blanking Time                      |                                                                                                                                                                                                                           |   |                                               | 450            |                                        | ns                               |

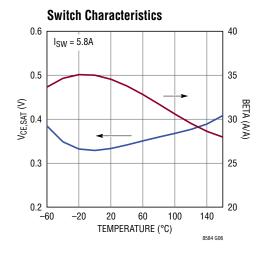

| Switch V <sub>CESAT</sub>                        | I <sub>SW</sub> = 4A                                                                                                                                                                                                      |   |                                               | 200            |                                        | mV                               |

| Switch Leakage Current                           | $V_{SW} = 4.2V$<br>$V_{SW} = 4.2V$                                                                                                                                                                                        | • |                                               | 5              | 70<br>4                                | nA<br>μA                         |

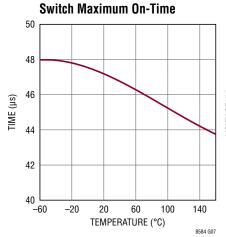

| Switch Maximum On Time                           |                                                                                                                                                                                                                           | • | 30                                            | 50             | 70                                     | μs                               |

| Switch Short Detection Timeout                   | Note 5                                                                                                                                                                                                                    | • | 0.5                                           | 0.85           | 1.2                                    | μs                               |

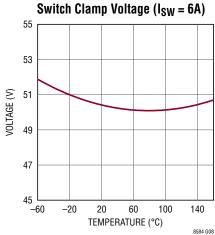

| Switch Clamp Voltage                             | I <sub>SW</sub> = 2mA<br>I <sub>SW</sub> = 6A                                                                                                                                                                             |   | 42                                            | 45<br>50       | 48                                     | V<br>V                           |

| Switch Clamp Blanking Time                       | Note 6                                                                                                                                                                                                                    |   | 80                                            | 200            | 360                                    | ns                               |

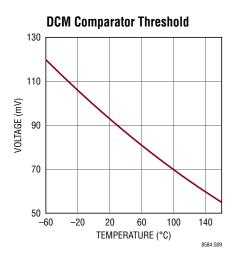

| DCM Comparator Trip Voltage                      | V <sub>SW</sub> – V <sub>VIN</sub>                                                                                                                                                                                        | • | 40                                            | 95             | 150                                    | mV                               |

| DCM Comparator Propagation Delay                 | 200mV Overdrive                                                                                                                                                                                                           | • |                                               | 100            | 180                                    | ns                               |

| DCM Blanking Time                                |                                                                                                                                                                                                                           |   |                                               | 230            |                                        | ns                               |

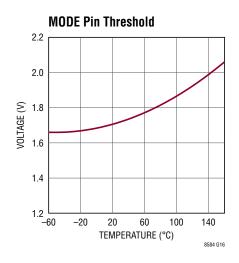

| MODE Threshold                                   |                                                                                                                                                                                                                           |   |                                               | 1.7            |                                        | V                                |

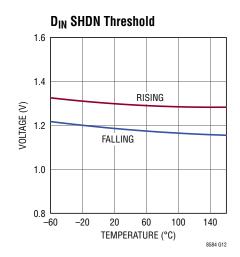

| D <sub>IN</sub> Shutdown Threshold               | High → Low, Referred to GND                                                                                                                                                                                               | • | 1                                             | 1.2            | 1.4                                    | V                                |

| D <sub>IN</sub> Shutdown Threshold Hysteresis    |                                                                                                                                                                                                                           |   |                                               | 100            |                                        | mV                               |

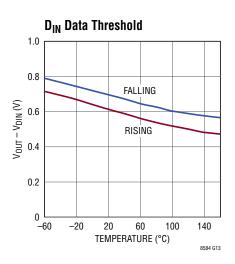

| D <sub>IN</sub> Data Threshold                   | High $\rightarrow$ Low, $V_{TH} = V_{OUT} - V_{DIN}$ , MODE = 0V                                                                                                                                                          | • | 0.3                                           | 0.7            | 0.9                                    | V                                |

| D <sub>IN</sub> Data Threshold Hysteresis        | $V_{TH} = V_{OUT} - V_{DIN}$ , MODE = 0V                                                                                                                                                                                  | • | 20                                            | 80             | 160                                    | mV                               |

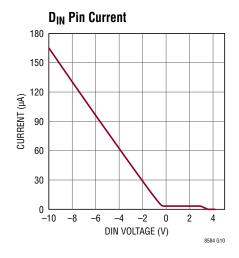

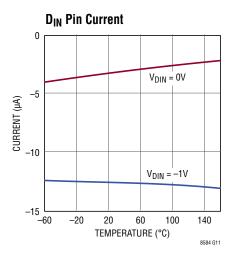

| D <sub>IN</sub> Pin Current                      | $V_{DIN} = 0V$<br>$V_{DIN} = -1V$                                                                                                                                                                                         | • | −6<br>−18                                     | −3<br>−14      | -1<br>-6                               | μΑ<br>μΑ                         |

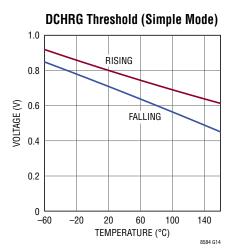

| DCHRG Threshold                                  | MODE Tied to V <sub>IN</sub>                                                                                                                                                                                              | • | 0.5                                           | 0.8            | 1.1                                    | V                                |

| DCHRG Hysteresis                                 | MODE Tied to V <sub>IN</sub>                                                                                                                                                                                              |   |                                               | 100            |                                        | mV                               |

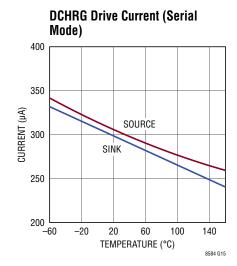

| DCHRG Pull-down Current                          | Pin Voltage = 0.4V                                                                                                                                                                                                        | • | 220                                           | 300            |                                        | μА                               |

| DCHRG Pull-up Current                            | Pin Voltage = V <sub>IN</sub> - 0.4V                                                                                                                                                                                      | • | 220                                           | 300            |                                        | μА                               |

| RMTR Pin High Voltage                            | $R_{RTMR} = 50k\Omega$                                                                                                                                                                                                    |   |                                               | 1.22           |                                        | V                                |

| RMTR Pin Low Voltage                             | $R_{RTMR} = 50k\Omega$                                                                                                                                                                                                    |   |                                               | 0              |                                        | V                                |

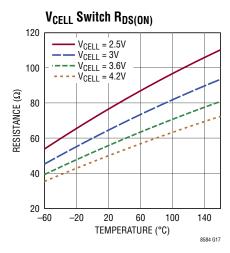

| V <sub>CELL</sub> Switch R <sub>DSON</sub>       |                                                                                                                                                                                                                           |   |                                               | 55             |                                        | Ω                                |

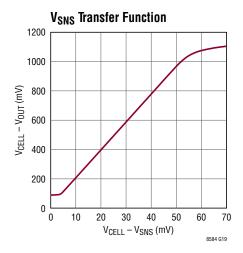

| V <sub>SNS</sub> Dynamic Input Range             | Gain Error ≤ 8%                                                                                                                                                                                                           | • | -30                                           |                | 70                                     | mV                               |

| V <sub>SNS</sub> Average Input Range             | Gain Error ≤ 3%                                                                                                                                                                                                           | • | 15                                            |                | 45                                     | mV                               |

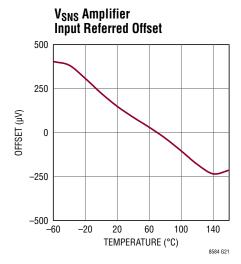

| V <sub>SNS</sub> Amplifier Input Referred Offset | V <sub>CELL</sub> – V <sub>SNS</sub> = 40mV                                                                                                                                                                               | • | -1.1                                          |                | 1.1                                    | mV                               |

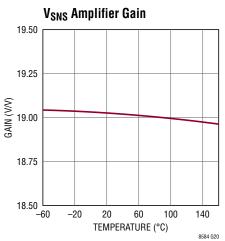

| V <sub>SNS</sub> Amplifier Gain                  | Over V <sub>SNS</sub> Average Input Range                                                                                                                                                                                 | • | 18.7                                          | 19             | 19.3                                   | V/V                              |

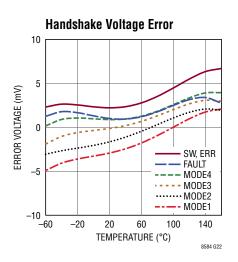

| Handshake Voltage Error                          | Measured ± with Respect to:  V <sub>MODE1</sub> = 0.2V  V <sub>MODE2</sub> = 0.4V  V <sub>MODE3</sub> = 0.6V  V <sub>MODE4</sub> = 0.8V  V <sub>SW,ERR</sub> = 1.2V  V <sub>FAULT</sub> = 1.4V  V <sub>FAULT</sub> = 1.4V | • | -13<br>-14<br>-18<br>-22<br>-31<br>-35<br>-28 |                | 13<br>14<br>18<br>22<br>31<br>35<br>28 | mV<br>mV<br>mV<br>mV<br>mV<br>mV |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C. $V_{IN} = 4.2V$ , $D_{IN} = GND$ unless otherwise noted. (Note 4)

| PARAMETER                                      | CONDITIONS                                        |   | MIN  | TYP   | MAX  | UNITS |

|------------------------------------------------|---------------------------------------------------|---|------|-------|------|-------|

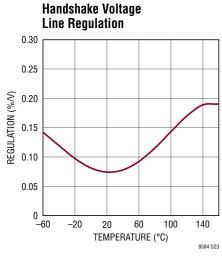

| Handshake Voltage Line Regulation              | From $V_{VIN} = 2.5V$ to $V_{VIN} = 4.2V$         |   |      | 0.2   | 0.75 | %/V   |

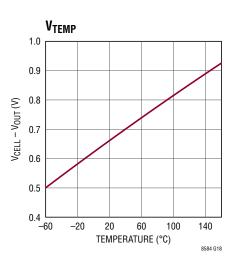

| V <sub>TEMP</sub> Temperature Coefficient (TC) | Note 7, $^{\circ}$ K = $(V_{CELL} - V_{TEMP})/TC$ |   |      | 2     |      | mV/°K |

| $V_{TEMP}$                                     | $V_{TEMP} = V_{IN} - V_{OUT}, T_J = 25^{\circ}C$  |   |      | 0.658 |      | V     |

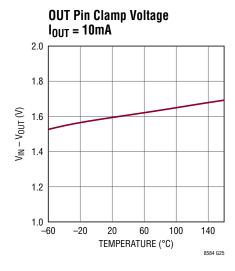

| OUT Pin Clamp Voltage                          | 10mA Sourced from Pin                             | • | 1.53 | 1.6   |      | V     |

| OUT Pin Amplifier Load Regulation              | I <sub>OUT</sub> = 10μA to 1mA                    | • | 0    | 0.2   | 0.4  | %/mA  |

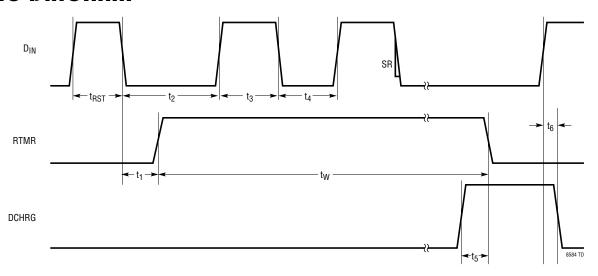

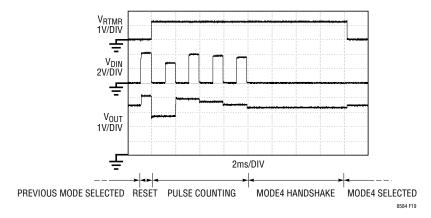

# **TIMING CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . MODE = 0V. Refer to Timing Diagram for parameter definition. (Note 4)

| SYMBOL           | PARAMETER                                       | CONDITIONS                                                                                    |   | MIN                       | TYP                         | MAX                         | UNITS                |

|------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------|---|---------------------------|-----------------------------|-----------------------------|----------------------|

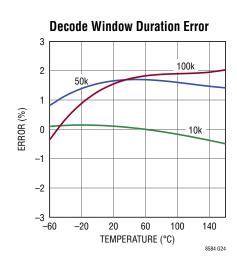

| t <sub>W</sub>   | Decode Window Duration                          | $R_{RTMR} = 10k\Omega$ $R_{RTMR} = 50k\Omega$ $R_{RTMR} = 100k\Omega$ $R_{RTMR} = 200k\Omega$ | • | 1.76<br>8<br>15.6<br>29.3 | 1.86<br>8.4<br>16.4<br>31.5 | 1.96<br>8.8<br>17.2<br>33.7 | ms<br>ms<br>ms<br>ms |

|                  | Decode Window Range                             |                                                                                               | • | 1.76                      |                             | 33.7                        | ms                   |

| t <sub>RST</sub> | D <sub>IN</sub> Serial Communication Reset Time |                                                                                               | • | 10                        |                             |                             | μs                   |

| t <sub>1</sub>   | RTMR Start-Up Time                              | $R_{RTMR} = 10k\Omega$                                                                        | • |                           | 1.8                         | 5                           | μs                   |

| $\overline{t_2}$ | D <sub>IN</sub> Hold-Off Time                   |                                                                                               | • | 50                        |                             |                             | μs                   |

| $t_3$            | D <sub>IN</sub> High Time                       |                                                                                               | • | 50                        |                             |                             | μs                   |

| $\overline{t_4}$ | D <sub>IN</sub> Low Time                        |                                                                                               | • | 50                        |                             |                             | μs                   |

| t <sub>5</sub>   | Discharger Activation Time                      | $R_{RTMR} = 10k\Omega$                                                                        |   |                           | 900                         |                             | ns                   |

| t <sub>6</sub>   | Discharger Deactivation Time                    |                                                                                               |   |                           | 2.1                         |                             | μs                   |

| SR               | D <sub>IN</sub> Slew Rate                       |                                                                                               | • | 9                         |                             |                             | V/ms                 |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Do not apply a positive or negative voltage or current source to RTMR, otherwise permanent damage may occur.

**Note 3:** ABSMAX rating refers to the maximum DC + AC leakage spike. Do not exceed  $40V_{DC}$  on any of the SW pins.

**Note 4:** The LT8584E is guaranteed to meet performance specifications from 0°C to 125°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization, and correlation with statistical process controls. The LT8584I is guaranteed over the full -40°C to 125°C operating junction temperature range. The LT8584H is guaranteed over the full -40°C to 150°C operating junction temperature range.

**Note 5:** This is a measure of time duration from the onset of the switch turning on to the time the short-circuit protection circuit is disabled. If the current comparator trips during this duration, the switch error latch is set. This indicates that the connection to the transformer primary is most likely shorted.

**Note 6:** This is a measure of time duration for the switch clamp to operate continuously without setting the switch error latch. If the switch clamp remains engaged longer than the switch clamp blanking time, the switch error latch is set and switching is disabled.

**Note 7:** The voltage proportional to temperature ( $V_{TEMP}$ ) is measured on the OUT pin while in analog multiplexer MODE 3 or 4.  $V_{TEMP}$  must be subtracted from the  $V_{CELL}$  voltage that is measured while in analog mux MODE 1. Both measurements should be taken within 100ms of each other to reduce errors in absolute temperature calculation.

LINEAR TECHNOLOGY

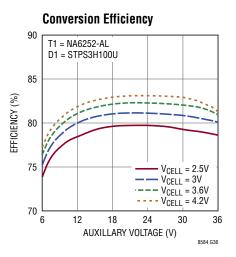

$T_A = 25$ °C,  $V_{IN} = V_{CELL} = V_{SNS} = 4.2$ V, unless otherwise noted.

$T_A = 25$ °C,  $V_{IN} = V_{CELL} = V_{SNS} = 4.2$ V, unless otherwise noted.

$T_A = 25$ °C,  $V_{IN} = V_{CELL} = V_{SNS} = 4.2$ V, unless otherwise noted.

$T_A = 25$ °C,  $V_{IN} = V_{CELL} = V_{SNS} = 4.2$ V, unless otherwise noted.

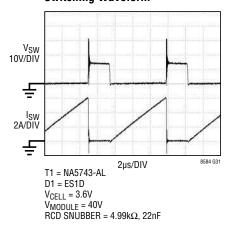

# Switching Waveform 10V/DIV T1 = NA5920-AL D1 = 2 SERIES ES1J

#### **Switching Waveform**

V<sub>CELL</sub> = 4.2V

V<sub>STACK</sub> = 400V

#### **Switching Waveform**

## PIN FUNCTIONS

**GND (Pin1, Pin 2, Pin 3, Pin 4, Pin 17):** Must be soldered directly to local ground plane.

**MODE (Pin 5):** Serial Enable Pin. Connect this pin to ground to enable serial interface for analog mux control. Connect this pin to  $V_{IN}$  to disable the analog mux. When the analog mux is disabled, the OUT pin defaults to  $V_{TEMP}$  measurement. Do not float this pin.

**RTMR (Pin 6):** Serial Interface Timer Pin. Place a resistor from this pin to ground to set the serial count duration window, t<sub>W</sub>. See the Applications Information section for proper resistor selection.

$D_{IN}$  (Pin 7): Data Input Pin. Take this pin to ground to initiate switching if MODE pin is connected to  $V_{IN}$ , or to select the desired analog mux state if MODE pin is tied to ground. This pin is designed to be directly driven from the LTC680x family's S pins.

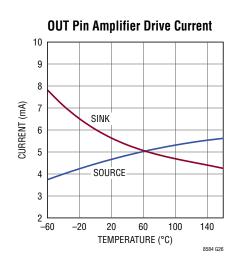

**OUT (Pin 8):** Analog Output Pin. Connect this pin to an accurate voltage monitor to measure a voltage proportional to the internal IC temperature,  $V_{TEMP}$ , if MODE pin is connected to  $V_{IN}$ , or measure the output of the internal analog mux if MODE pin is connected to ground. In analog mux mode, the OUT pin allows voltage monitoring of the  $V_{CELL}$  pin, the  $V_{SNS}$  pin, or  $V_{TEMP}$ . This pin is designed to be directly connected to the LTC680x family's C pins. Must connect a compensation capacitor to this pin. See the Applications Information section for proper capacitor sizing and placement.

**V**<sub>IN</sub> (**Pin 9**): Supply Pin. Connect this pin directly to the positive battery cell terminal. Must be bypassed with high grade (X5R or better) ceramic capacitor placed close to the transformer's primary winding connection.

**V<sub>CELL</sub>** (**Pin 10**): Cell Voltage Monitor Pin. This pin provides a Kelvin connection to the battery cell for accurate voltage monitoring. Connect this pin directly to the positive battery cell terminal. The recommended cell voltage is 2.5V to 5.3V.

$V_{SNS}$  (Pin 11): Voltage Sense Pin. Connect this pin to the current sense resistor connected to the primary side of the transformer. Use this pin to measure average current discharged from battery cell (see the Block Diagram). MODE pin must be connected to ground and the internal analog mux must have the  $V_{SNS}$  pin selected to use this feature. Input current is determined as  $(V_{VCELL} - V_{VSNS})/R_{SNS}$ .

**DCHRG (Pin 12):** Discharge Pin. The Discharge pin can be configured as an input or output pin. Connect MODE pin to ground to configure DCHRG as an output pin where DCHRG is driven to  $V_{IN}$  during switching and driven to ground when switching is deactivated. The output configuration can be used to drive multiple LT8584's or other switching regulators in parallel, to boost discharge capability. Connect MODE pin high to configure DCHRG as an input. When configured as an input pin, drive DCHRG pin to  $V_{IN}$  to enable switching. Note in this mode that serial communication is disabled and the  $D_{IN}$  pin must be grounded to initiate switching.

**SW** (Pin 13, Pin 14, Pin 15, Pin 16): Switch Pin. This is the collector of the internal 6A NPN power switch. Minimize the metal trace area connected to this pin to minimize EMI. Connect the bottom side of the transformer primary to this pin.

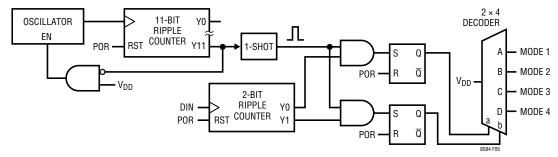

BLOCK DIAGRAM

#### CELL ABOVE R<sub>SNS</sub> MODULE+ CTRAN $C_{VCELL}$ V<sub>MODULE</sub> MODULE- $V_{SNS}$ V<sub>SNS</sub> AMP SWITCH PROTECTION CIRCUITRY TO ANALOG MUX 19x CURRENT COMPARATOR Q R SWITCH : LATCH **≤** 6.3mΩ 95mV DCM COMPARATOR 40mV CHIP SERIAL MODE POWER TO PARALLEL DISCHARGERS (OPTIONAL) **DCHRG** V<sub>CELL</sub> CHIP ENABLE **OUT PIN CLAMP** SIMPLE CELL BEING BALANCED MODE MODE 1.22V CONTROL LOGIC TO C PIN LTC680x LATCH POWER DURING TIMER OUT 11-BIT COUNTER RTMR TIMER COUT $V_{CELL}$ GND V<sub>SNS</sub> AMP \_\_\_\_ ANALOG MUX TEMPERATURE **CELL BELOW** TO S PIN (LTC680x)

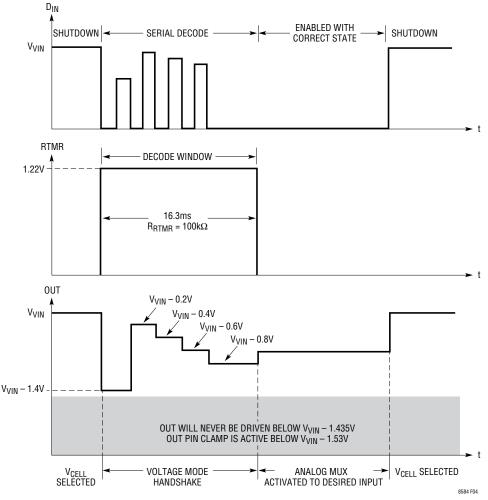

## TIMING DIAGRAM

## **OPERATION**

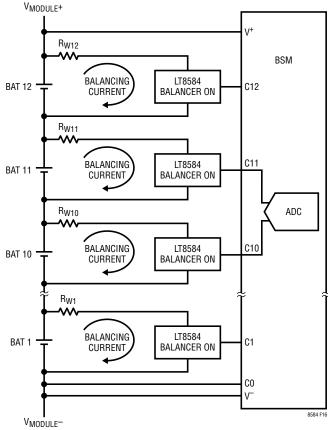

Many systems use multiple battery cells connected in series to increase the available capacity and voltage. In such systems, the individual battery cells must be constantly monitored to ensure that they operate within a controlled range. Otherwise, the battery's capacity and life span may be compromised. Linear Technology offers the LTC680x family series of multicell battery stack monitors (BSM) to accomplish this task.

The LTC680x monitors each individual cell in the stack and communicates this information through a proprietary serial bus to a central processing unit. As a cell begins to reach the upper charge limit, commands are issued to the LTC680x to turn on that cell's passive shunt, bypassing the charging current to that cell and allowing the current to continue to the rest of the cells. The passive shunt current and/or power capability constrains the maximum charging current for the battery stack. Using a passive shunt is also inefficient, and the shunted current produces considerable heat at higher charging currents.

The LT8584 solves the two limitations of passive shunting balancers by actively shunting the charging current and returning the energy back to the battery stack. Instead of the energy being lost as heat, it is reused to charge the rest of the batteries in the stack. The architecture of the LT8584 also solves the problem of reduced run time when one or more of the cells in the stack reaches the lower safety voltage threshold before the entire stack capacity

is extracted. Only active balancing can redistribute the charge from the stronger cells (cells with higher voltage) to charge the weaker cells. This allows the weaker cells to continue to supply the load, extracting greater than 96% of entire stack capacity where passive balancing may only extract 80%.

The LT8584 has an integrated 6A switch designed to operate as a boundary mode flyback converter and provides 2.5A average discharge current. The average discharge current is also scalable by using multiple LT8584s to balance each cell. Note that each battery in the stack requires an LT8584 active cell balancer.

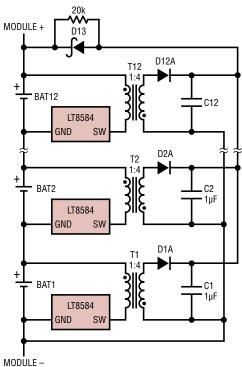

The LT8584 flyback topology allows the charge to return between any two points in the battery stack. Most applications use a module approach and return the charge to a local set of 12 series-connected cells monitored by a 12 channel BSM IC, where the output of the flyback converter is designated as  $V_{MODULE}$ . The entire battery stack is then constructed using several 12-cell modules connected in series. A second approach is to return the charge to the entire battery stack, where the flyback output is designated as  $V_{STACK}$ . A final option is to return the charge to an auxiliary power rail, designated as  $V_{AUX}$ .

The LT8584 has two modes of operation—selectable by the MODE pin—that can be integrated with the LTC680x or other battery stack system. In simple mode, the LT8584

LINEAR

discharger is toggled on/off using a logic input pin. In serial mode, the LT8584 allows the user to measure the discharge current and the die temperature, in addition to the cell voltage.

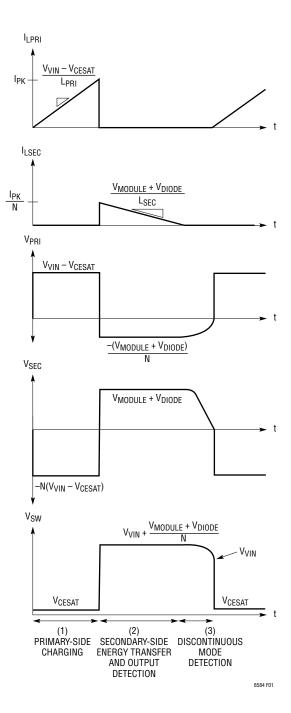

#### GENERAL FLYBACK OPERATION

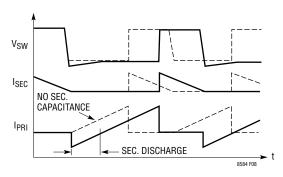

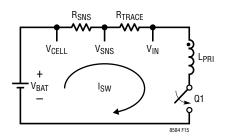

The first cycle will commence approximately 2µs after LT8584 has been commanded to discharge a cell. The LT8584 is configured as a flyback converter operating in boundary mode (the edge of continuous operation), and has three basic states (see Figure 1).

#### 1. Primary-Side Charging

When the switch latch is set, the internal NPN switch turns on, forcing  $(V_{VIN}-V_{CESAT})$  across the primary winding. Consequently, current in the primary coil rises linearly at a rate of  $(V_{VIN}-V_{CESAT})/L_{PRI}$ . The input voltage is mirrored on the secondary winding as  $-N \bullet (V_{VIN}-V_{CESAT})$  which reverse-biases the secondary-side series diode and prevents current flow in the secondary winding. Thus, energy is stored in the core of the transformer.

#### 2. Secondary-Side Energy Transfer

When current limit is reached, the current limit comparator resets the switch latch and the device enters the second phase of operation, secondary-side energy transfer. The energy stored in the transformer core forward-biases the series diode and current flows into the output capacitor and/or battery. During this time, the output voltage plus the diode drop is reflected back to the primary coil.

#### 3. Discontinuous Mode Detection

During secondary-side energy transfer to the output capacitor,  $(V_{MODULE} + V_{DIODE})/N$  will appear across the primary winding. A transformer with no energy cannot support a DC voltage, so the voltage across the primary winding will decay to zero. In other words, the collector of the internal NPN, SW pins, will ring down from  $V_{VIN} + (V_{MODULE} + V_{DIODE})/N$  to  $V_{VIN}$ . When the SW pin voltage falls below  $V_{VIN} + 95\text{mV}$ , the DCM comparator sets the switch latch and a new switch cycle begins. States 1-3 continue until the part is disabled.

Figure 1. Simplified Discharging Waveforms

LINEAR TECHNOLOGY

#### SWITCH PROTECTION

Several protection features are included to reduce the likelihood of permanent damage to the internal power NPN switch: the short-circuit detector, the high-impedance detector, the switch overvoltage protection (OVP), and internal undervoltage lockout (UVLO). These also alert the user when the integrity of the discharge converter has been compromised because of a fault. Switching is disabled during fault conditions.

#### **Short-Circuit Detector**

The short-circuit detector detects when the power NPN switch turns off prematurely due to a short in the primary-side winding. If the current comparator trips before the 850ns short detection timeout, the switch error latch will trip. The OUT pin is driven to  $V_{VIN}-1.2V,\,V_{SW,ERR},\,during$  a switch error. The part must be reset to clear the switch error fault.

## **High-Impedance Detector**

The high-impedance detector monitors how long the power NPN switch has been on. If the switch remains on longer than 50 $\mu$ s, the switch maximum on-time, the switch error latch is set and the OUT pin is driven to V<sub>VIN</sub>-1.2V, V<sub>SW,ERR</sub>. The part must be reset to clear the switch error fault.

### Overvoltage Protection (OVP)

The OVP circuitry dynamically clamps the NPN collector's SW pins to 50V. This protects the internal power switch from entering breakdown and causing permanent damage. The clamp is also used as a primary-side snubber to absorb the leakage inductance energy. The 200ns switch clamp blanking time determines if the clamp is absorbing a leakage spike or if the switch is turning off while the secondary of the transformer is open. If the switch clamp is on longer than approximately 200ns, the switch error latch is set. The part must be reset to clear the switch error fault.

## Internal Undervoltage Lockout (UVLO)

LT8584 protects itself during a UVLO condition by disabling switching. The OUT pin is driven to  $V_{VIN}-1.4V$ ,  $V_{FAULT}$ , during a UVLO condition. A UVLO fault is non-latching and dominates over a switch fault (Serial Mode requires  $V_{IN}$  to remain above 2V for a UVLO fault to be non-latching). Once the UVLO condition is cleared, the OUT pin reverts to normal operation and switching resumes. If the switch fault latch was tripped prior to the UVLO event, the OUT pin will indicate a switch fault,  $V_{SW,ERR}$ , only after the UVLO condition is cleared and switching would remain disabled.

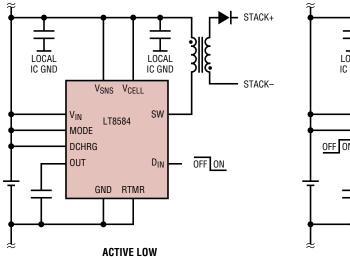

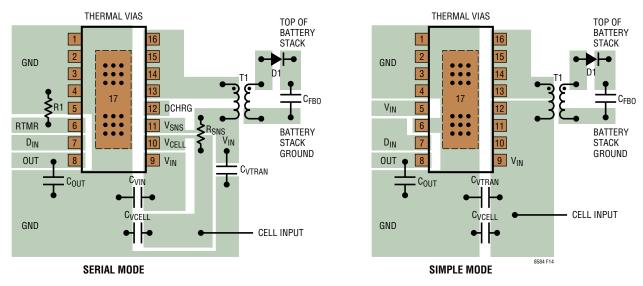

Figure 2. Simple Mode Configurations

#### SIMPLE MODE OPERATION

Connecting the MODE pin to the  $V_{IN}$  pin configures the LT8584 as a simple discharger with a simple on/off shutdown pin. Two shutdown options are provided to handle either an active high (DCHRG) or an active low input ( $D_{IN}$ ), see Figure 2. Connect  $D_{IN}$  to ground and use DCHRG pin for an active high input, or connect DCHRG to  $V_{IN}$  and use  $D_{IN}$  as an active low input. The part will begin switching once the  $D_{IN}$  pin is low and DCHRG is high. Figure 3 shows the enable logic function. Never drive  $D_{IN}$  more than 0.4V below the local ground while operating in active-high simple mode.

Figure 3. Simple Mode Enable Logic

#### **OUT Pin in Simple Mode**

The OUT pin defaults to  $V_{TEMP}$ , a voltage proportional to the die temperature, and is measured with respect to the cell voltage such that  $V_{TEMP} = V_{VCELL} - V_{OUT}$ . This can be used to monitor the internal die temperature for system diagnostics. The OUT pin will also output two distinct indication voltage levels,  $V_{VIN} - 1.4V$ ,  $V_{FAULT}$ , for an internal UVLO condition, or  $V_{VIN} - 1.2V$ ,  $V_{SW,ERR}$ , for a switch error.  $V_{TEMP}$  is not allowed to exceed 1V (equivalent to  $180^{\circ}\text{C})^{1}$ . This makes both the fault and switch error voltages deterministic. The switch error latch is set when the power NPN switch has encountered a fault (see the Switch Protection section for more details).

<sup>&</sup>lt;sup>1</sup> Not verified during production testing.

Figure 4. Serial Communication Decode

8584fh

Figure 5. Serial Communication Architecture

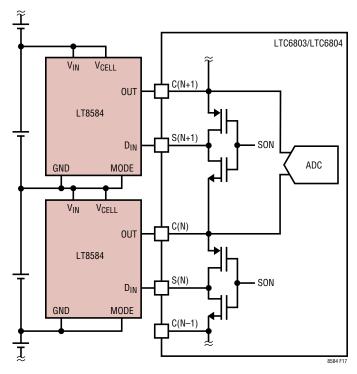

#### **SERIAL MODE OPERATION**

Use serial mode if monitoring the discharging current and/or the die temperature are required. Connecting the MODE pin to GND enables serial communication. The  $D_{IN}$  pin is used to input serial data through a custom serial bus (see Figures 4 and 5).

#### **Serial Mode Safety Features**

The LT8584 provides the user with several levels of safety and verification. The LT8584 has built in switch protection that detects and halts power delivery during either a primary-side open or short, a secondary-side open or short, or an overvoltage on the primary or secondary. The LT8584 outputs the  $V_{SW,ERR}$  handshake that can be read back by the battery stack monitor (BSM).

The LT8584 also detects communication errors including too many or too few  $D_{\text{IN}}$  pulses or a UVLO condition. The LT8584 outputs the  $V_{\text{FAULT}}$  handshake that can be read back by the BSM.

The LT8584 also provides critical cell parameters including temperature, discharge current, cell voltage, and cell and connection DC resistance. These are all read back by the BSM. As the cell starts to age, the cell impedance increases. This allows the user to perform preventative maintenance, keeping the system down time to a minimum.

Finally, the LT8584 handshake voltages are ±3% accurate independent references that can be used to verify that every channel in the BSM is measuring accurately.

#### **Serial Architecture**

Power to the part is latched on the first negative edge of  $D_{\text{IN}}$  signal and remains latched for the duration of the decode window,  $t_{\text{W}}$ . This allows the  $D_{\text{IN}}$  pin to be toggled for communicating serial data without resetting the part.

The LT8584 counts the number of negative edges seen on the  $D_{\text{IN}}$  pin. Note that the first edge, which initiates serial communication and latches the part, is not counted. There are four active modes the user can select as shown in Table 1. Handshaking is accomplished by reading the analog voltage on the OUT pin. Handshaking voltages are asserted on the negative edge of the  $D_{\text{IN}}$  signal, corresponding to the serial decode count.

Once the decode window expires and RTMR pin returns to ground, three actions are initiated: the OUT pin analog multiplexer switches to the desired measurement, the discharger turns on depending on selected mode in Table 1, and the input power latch disables. Note that the LT8584 can only be disabled after the decode window has expired and the  $D_{\text{IN}}$  pin has been taken high.

**Table 1.Serial Mode States**

| PULSE<br>COUNT | MODE  | DISCHARGER<br>STATE | MUX<br>OUTPUT      | HANDSHAKE<br>VOLTAGE<br>(V <sub>VIN</sub> – V <sub>OUT</sub> ) |

|----------------|-------|---------------------|--------------------|----------------------------------------------------------------|

| Part Disabled  | 0     | Disabled            | $V_{CELL}$         | N/A                                                            |

| 0              | Fault | Disabled            | $V_{FAULT}$        | 1.4                                                            |

| 1              | 1     | Enabled             | $V_{CELL}$         | 0.2                                                            |

| 2              | 2     | Enabled             | $V_{SNS}$          | 0.4                                                            |

| 3              | 3     | Enabled             | $V_{TEMP}$         | 0.6                                                            |

| 4              | 4     | Disabled            | $V_{TEMP}$         | 0.8                                                            |

| ≥5             | Fault | Disabled            | V <sub>FAULT</sub> | 1.4                                                            |

#### Serial Timer Decode Window

The timer initiates on the first negative edge on the  $D_{IN}$  pin. RTMR pin remains high for the duration of the timer which signifies the decode window for the serial input counter. A resistor from the RTMR pin to ground sets the decode window duration. The duration can be accurately set from 1.9ms ( $R_{RTMR} = 10k$ ) to 31ms ( $R_{RTMR} = 200k$ ). The timer can be set outside this range, but the accuracy decreases. The serial input counter stops counting and latches the data once the RTMR pin goes low; after which, the OUT pin amplifier input MUX selects the desired measurement, and the discharger is set to the right state.

#### **Serial Communication Fault Modes**

The serial interface has several fault monitors that prevent entering undesired modes due to a communication error. The OUT pin is set to  $V_{VIN}-1.4V$  to indicate the LT8584 is in fault. The part remains in fault from the onset of RTMR going high until the first count is detected. If no count is seen by the serial input counter during the decode window, the fault is latched. If the serial input counter counts higher than 4 negative edges, the fault latch is set.

A third latching fault occurs if an internal undervoltage lockout (UVLO) is detected during the decode window. This protects against undesired operation if data latches or the serial input counter were reset. The part must be reset by taking  $D_{\text{IN}}$  high to clear a fault.

#### **DIN Pin and Serial Bus Timing**

Several internal passive filters are added to the data bus to prevent injected system noise corrupting serial communication. These filters have time constants that place constraints on the serial communication timing requirements (see the Timing Diagram). The LT8584 can reject up to 4 $\mu$ s of erroneous glitches on the D<sub>IN</sub> pin in either direction. The power latch filter can also reject up to a 4 $\mu$ s glitch on D<sub>IN</sub>.

The  $D_{IN}$  pin has built-in hysteresis of approximately 100mV. This allows the serial input counter to recognize both slow and fast edges without erroneous behavior. The discharger activation or deactivation time is typically less than  $3\mu s$  and is a direct indication of the switch enable latch state.

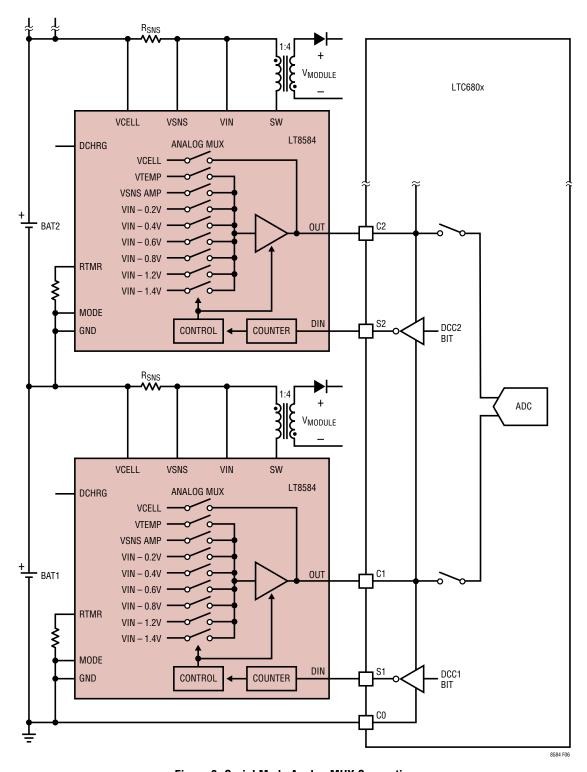

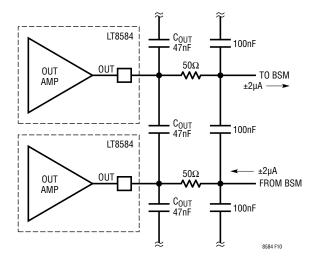

#### **OUT Pin Analog MUX**

An internal multiplexer, MUX, selects between  $V_{CELL}$  and the OUT pin amplifier based on one of the selected Serial Modes shown in Table 1. The OUT pin amplifier has a  $5k\Omega$  internal load and has several inputs including:  $V_{TEMP}$ , the  $19^{\bullet}V_{SNS}$  amplifier, and six handshake voltages. The internal MUX defaults to  $V_{CELL}$  in shutdown—consuming no power in the process—and provides a  $55\Omega$  nominal resistance from the  $V_{CELL}$  pin to the OUT pin. Figure 6 shows the connection of the OUT pin to a BSM and its internal analog MUX.

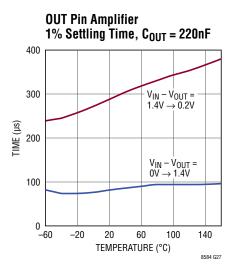

The MUX switches over to one of the handshake voltage levels once both the LT8584 and the decode window are activated. The OUT amplifier will indicate a fault at start-up until the serial input counter recognizes the first negative edge on  $D_{\text{IN}}$ . Subsequent negative edges on  $D_{\text{IN}}$  cause the MUX to select the handshake voltage corresponding to the number of edges counted. These voltage levels provide a means of verifying if the serial interface has recognized the correct count. Note that the OUT pin amplifier has an approximate 200 $\mu$ s one percent settling time when driving a 220nF load capacitance.

Once the RTMR pin goes low, the MUX selects the OUT pin mode corresponding to the number of serial input counts (see Table 1 for available modes). The part can also be placed in shutdown when RTMR is low and the decode window has expired.

#### **V<sub>CELL</sub>** Measurement

The user can measure the cell voltage by measuring the voltage on the OUT pin either with the part disabled (discharger off) or with the part enabled in MODE 1 (discharger on), see Table 1. The LT8584 uses an internal PMOS switch with  $R_{DSON}=55\Omega$  to connect  $V_{CELL}$  to the OUT pin. Note that any current flowing into or out of the OUT pin will cause a measurement error due to the IR drop across the switch.

#### V<sub>SNS</sub> 19× Amplifier

An amplifier is provided to allow the user to monitor the discharger current. This measurement can only be performed when the discharger is on (MODE 2). The differential voltage between  $V_{VCELL}$  and  $V_{VSNS}$  is amplified 19×.

Figure 6. Serial Mode Analog MUX Connection

Downloaded from: http://www.datasheetcatalog.com/

This reduces errors due to input offset in the measurement circuitry connected to the OUT pin. It also allows the use of low-value resistors, and thus, yields greater overall efficiency.

For accuracy, the  $V_{IN}$  pin should be tied to the  $V_{SNS}$  pin to include both the LT8584 bias current and the internal NPN base drive current. Tying the  $V_{IN}$  pin to the  $V_{SNS}$  pin changes the overall gain to 20x. Tying the  $V_{IN}$  pin to the  $V_{CELL}$  measures transformer current only and the overall gain remains 19x.

The  $V_{SNS}$  amplifier has a -30 mV to 70 mV dynamic input range. Internal filtering and circuit architecture allows accurate measurements even when the input current contains negative components. The  $V_{SNS}$  amplifier requires that the average input current remain positive.  $V_{VIN} - V_{OUT}$  is not allowed to exceed 1V during  $V_{SNS}$  measurement to guarantee that both  $V_{FAULT}$  and  $V_{SW,ERR}$  are deterministic. This sets the maximum average input range,  $V_{VCELL} - V_{VSNS}$ , to 50 mV.

## **Die Temperature Output**

The user can also monitor the die temperature by selecting either MODE 3 (discharger enabled) or MODE 4 (discharger disabled). The voltage  $V_{VCELL} - V_{OUT}$ ,  $V_{TEMP}$ , is proportional to the absolute temperature in degrees Kelvin. Thus, the user needs to take two measurements to calculate the die temperature. Temperature data gives the user a second means to verify if the discharger is on as well as to monitor environmental conditions.  $V_{TEMP}$  is not allowed to exceed 1V (equivalent to 180°C)<sup>1</sup> to make both  $V_{FAULT}$  and  $V_{SW,ERR}$  deterministic.

The following equation is used to determine the internal die temperature in degrees Celsius:

$$T_J(^{\circ}C) = \frac{V_{TEMP} - 0.609}{0.00197}$$

where  $V_{TEMP} = V_{VCELL} - V_{OUT}$  and expressed in volts. Although the absolute die temperature can deviate from the above equation by  $\pm 25^{\circ}C$ , the relationship between  $V_{TEMP}$  and the change in die temperature is well defined. The offset error can be calibrated out using an accurate system temperature monitor like that in the LTC680x family of parts. There is also a small  $V_{VCELL}$  dependence on  $V_{TEMP}$  which can be corrected using the following expression:

$$T_{J.CORR}$$

(°C) =  $T_{J.CAL}$  + (4.2V -  $V_{CELL}$ ) • 2°C

where  $T_{J,CORR}$  is the corrected die temperature and  $T_{J,CAL}$  is die temperature calculated from the previous equation.

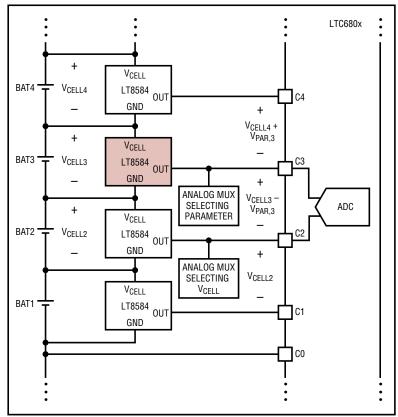

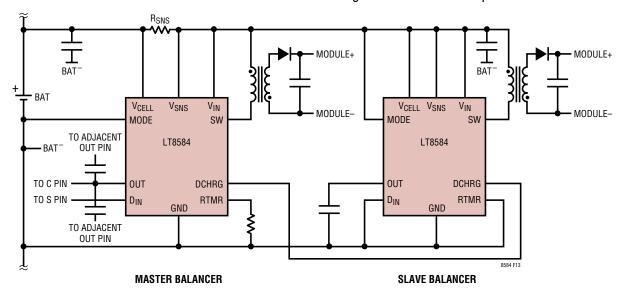

#### **Serial Mode Differential Measurements**

All parameters including handshake voltages,  $V_{SNS}$ , and  $V_{TEMP}$  are extracted differentially by taking two sequential measurements and doing a subtraction. Figure 7 shows the method for extracting a given parameter,  $V_{PAR}$ , from the highlighted LT8584. The LT8584 directly below the LT8584 under measurement must be forced to select  $V_{CELL}$  (MODE 0) and becomes the negative reference for both sequential measurements.

**Table 2. MODE Selection During Differential Measurements**

|                                       | SERIAL MODE STATE |                         |  |  |  |

|---------------------------------------|-------------------|-------------------------|--|--|--|

| DESIRED PARAMETER                     | 1ST MEASUREMENT   | 2ND MEASUREMENT         |  |  |  |

| Handshake Voltage                     | MODE 0            | During Decode<br>Window |  |  |  |

| V <sub>SNS</sub>                      | MODE 1            | MODE 2                  |  |  |  |

| V <sub>TEMP</sub> , Balancer Enabled  | MODE 1            | MODE 3                  |  |  |  |

| V <sub>TEMP</sub> , Balancer Disabled | MODE 0            | MODE 4                  |  |  |  |

Selecting  $V_{CELL}$  for the first measurement is performed by entering either MODE 0 (balancer disabled) or MODE 1 (balancer enabled). Use Table 2 to determine which  $V_{CELL}$  to reference for a given parameter. All measurements are taken after the decode window has expired, unless otherwise noted.

$$V_{PAR}$$

= 1st Measurement – (2nd Measurement)

=  $V_{CELL} - (V_{CELL} - V_{PAR})$

The LTC6803's channel above the channel under measurement will have a voltage higher than a standard cell,  $V_{CELL} + V_{PAR}$ , see Figure 7. The LT8584 was architected to protect the LTC6803's ADC inputs and to guarantee that they well never be stressed beyond their absolute maximum rating.

#### **DCHRG Output**

The DCHRG pin allows the LT8584 to operate several dischargers in parallel. The DCHRG pin goes high when the switch enable latch is set. The DCHRG pin can be used to directly drive the DCHRG pin of another LT8584 configured in simple mode (MODE pin connected to  $V_{IN}$ ) or to directly drive the shutdown pin of another power converter. It has the ability to sink or source currents up to  $300\mu A$ .

<sup>&</sup>lt;sup>1</sup> Not verified during production testing.

#### **MEASUREMENT 1 (V<sub>CELL</sub>)** LTC680x $V_{CELL}$ LT8584 OUT BAT4 🛨 $V_{\text{CELL4}}$ C4 GND $V_{CELL4}$ V<sub>CELL</sub> LT8584 OUT BAT3 BAT3 🛨 $V_{CELL3}$ GND ANALOG MUX SELECTING $V_{CELL3}$ ADC + $V_{CELL}$ $V_{CELL}$ LT8584 OUT $V_{CELL2}$ GND ANALOG MUX SELECTING V<sub>CELL2</sub> $V_{CELL}$ $V_{CELL}$ LT8584 OUT BAT1 BAT1 C1 GND

## $MEASUREMENT\ 2\ (V_{CELL}-V_{PAR})$

Figure 7. Serial Mode Differential Measurements

The LT8584 can be used as a discharger for balancing the charge in battery or supercapacitor stack systems. The user can choose either simple mode or serial mode. The LT8584 can be driven from any battery stack monitor such as the LTC680x. Simple mode can be employed using either active high or active low logic, increasing its interface flexibility.

#### COMPONENT SELECTION

Few external components are required to achieve balancing. The only external components are the transformer, the output diode(s), the  $V_{IN}$  bypass capacitors, the  $R_{SNS}$  resistor (for measuring discharge current), the  $R_{RTMR}$  resistor (for serial mode), and in some cases, a RCD snubber.

The equations are shown for a module based approach described in the Operation section.  $V_{MODULE}$  becomes  $V_{STACK}$  in all equations for applications returning charge to the entire stack voltage, and  $V_{MODULE}$  becomes VAUX for all applications returning charge to an auxiliary power rail.

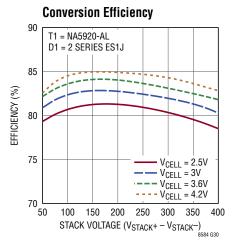

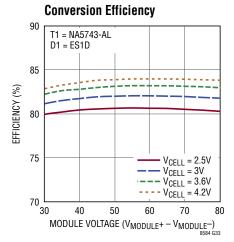

## Transformer Design

The transformer design should yield overall converter efficiencies greater than 80%. This reduces heat dissipation and allows for a smaller converter PCB footprint. A proper transformer design balances core losses with winding losses. The LT8584 converter operates in DCM where the flux swing in the transformer is the greatest. This shifts most of the heat loss from winding loss to core loss. Reduce transformer core flux swing by lowering the air-gap permeability. A lower permeability requires more

turns to achieve a desired primary inductance; thus, a balance can be achieved between core and winding losses. Recommended transformers are given in Table 3 that have been optimized for efficiency and size. Use the following guidelines when designing new transformers.

Reduce the transformer size by designing the boundary-mode operating frequency between 100kHz and 150kHz. The peak primary current is fixed at 6A by the chip. The transformer turns ratio, N, should be selected by optimizing the converter input RMS current, i.e. battery discharge current. The RMS input current can be estimated as:

$$I_{\text{RMS,IN}} = I_{\text{PK}} \bullet \sqrt{\frac{f_{\text{BM}} \bullet t_{\text{ON}}}{3}}$$

Note that negative switch current reduces the RMS input current by effectively reducing the boundary-mode frequency,  $f_{\rm BM}$ , (see Figure 8). Reduce the overall reflected capacitance on the SW node by reducing the output diode and transformer interwinding parasitic capacitances.

Figure 8. Effect of Secondary Winding Capacitance

**Table 3. Recommended Transformers**

| MANUFACTURER                                | PART NUMBER                                      | RECOMMENDED<br>OUTPUT RANGE (V)    | RCD SNUBBER<br>REQUIRED | SIZE W × L × H (mm)                                                     | L <sub>PRI</sub> (µH) | TURNS RATIO (PRI:SEC) |

|---------------------------------------------|--------------------------------------------------|------------------------------------|-------------------------|-------------------------------------------------------------------------|-----------------------|-----------------------|

| Coilcraft<br>www.coilcraft.com              | NA6252-AL<br>NA5743-AL<br>NA5920-AL*             | 10 to 35<br>30 to 80<br>100 to 400 | Yes<br>Yes<br>No        | 15.24 × 12.7 × 11.43<br>15.24 × 12.7 × 11.43<br>15.24 × 12.7 × 11.43    | 4<br>4<br>4           | 11:15<br>1:4<br>1:24  |

| Cooper Bussmann<br>www.cooperindustries.com | CTX02-19175-R<br>CTX02-19174-R<br>CTX02-19176-R* | 10 to 35<br>30 to 80<br>100 to 400 | Yes<br>Yes<br>No        | 15 × 13 × 12<br>15 × 13 × 12<br>15 × 13 × 12                            | 4<br>4<br>4           | 3:4<br>1:4<br>1:24    |

| Würth<br>www.we-online.com                  | 750314019_R01<br>750314018_R02<br>750314020_R01* | 10 to 35<br>30 to 80<br>100 to 400 | Yes<br>Yes<br>No        | 15.24 × 13.34 × 11.43<br>15.24 × 13.34 × 11.43<br>15.24 × 13.34 × 11.43 | 4<br>4<br>4           | 3:4<br>1:4<br>1:24    |

<sup>\*</sup> Switch error latch may trip when starting at voltages lower than the recommended output range.

NEAD

The RMS input current can be increased by increasing the ratio between the effective switch on-time,  $t_{ON}$ , and off-time,  $t_{OFF}$ . This off-time ratio is set by the transformer ratio, N. The following equation sets the switch off-time to approximately 1/3 of the switch on-time to optimize power transfer and efficiency.

$$N = \frac{Secondary\ Turns}{Primary\ Turns} = \frac{V_{MODULE}}{3 \bullet V_{IN}}$$

The off-time ratio should not be decreased much beyond 1/5; otherwise, secondary-side energy transfer time becomes too short, and the converter efficiency is reduced. Some applications may require a lower RMS current due to charging limitations or thermal dissipation limitations. Both can be reduced by increasing the turns ratio, N. Use the following equation to size the transformer's primary inductance:

$$L_{PRI} = \frac{1}{I_{PK} \cdot f_{BM} \cdot \left(\frac{1}{V_{IN}} + \frac{N}{V_{MODULE}}\right)}$$

Keep the primary inductance in the range of  $2.2\mu H$  to  $10\mu H$ . The lower limit guarantees proper detection of an open circuit in the transformer's secondary. The upper limit guarantees the high-impedance detector does not activate a false switch error during normal operation.

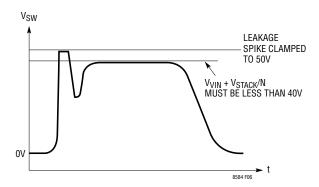

#### Leakage Inductance

Leakage inductance causes added voltage stress on the internal power NPN collector. The LT8584 uses an internal Zener clamp to absorb this leakage spike energy and clamp the switch node voltage to 50V. The leakage spike energy should be limited to improve efficiency. Figure 9 shows the waveform of the internal NPN switch.

Design the transformer to have minimum leakage inductance. Keep both transformer windings tightly wound around the core air gap. Using a bifilar winding or a sandwiched secondary decreases leakage inductance. Note that increased interwinding capacitance is a trade-off with lower leakage inductance. Several iterations may be required to optimize the transformer design.

Figure 9. Internal Switch Voltage Waveform

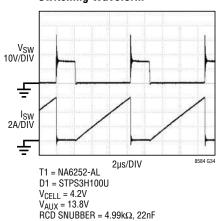

Higher transformer turns ratios benefit from higher reflected capacitance that helps snub the leakage spike. N ratios less than 8 usually require an RCD snubber to help clamp this primary-side leakage spike and increase the converter efficiency. Good values for the resistor and capacitor are  $4.99k\Omega$  and 22nF, respectively.

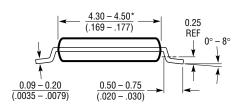

#### **Output Diode**

The output diode(s) are selected based on the maximum repetitive reverse voltage ( $V_{RRM}$ ) and the average forward current,  $I_{F(AVG)}$ . The output diode's  $V_{RRM}$  should at a minimum exceed  $V_{MODULE} + N \cdot V_{VIN}$ . The LT8584's internal OVP circuitry triggers at 50V, and  $V_{RRM}$  should therefore exceed  $N \cdot (50 + V_{VIN})$  to prevent damage to the output diode during an OVP event. Note that the leakage spike will usually cause the OVP to trigger roughly 10% lower than the nominal reflected voltage on the primary. The output diode's  $I_{F(AVG)}$  should exceed  $I_{PK}/2N$ , the average short-circuit current. The average diode current is also a function of the output voltage.

$$I_{F(AVG)} = \frac{I_{PK} \bullet V_{VIN}}{2 \bullet (V_{MODULE} + N \bullet V_{VIN})}$$

The highest average diode current occurs at low output voltages and decreases as the output voltage increases. Reverse recovery time, reverse bias leakage, and junction capacitance should also be considered. All affect the overall charging efficiency. Excessive diode reverse recovery times can cause appreciable discharging of the output stack, thereby decreasing charge recovery. Choose a diode with a reverse recovery time of less than 75ns.

Diode leakage current under high reverse bias bleeds the output battery/capacitor stack of charge. Choose a diode that has minimal reverse bias leakage current. Diode junction capacitance is reflected back to the primary, and energy is lost during negative NPN collection conduction. Choose a diode with minimal junction capacitance. Table 4 recommends several output diodes for various output voltages that have adequate reverse recovery times.

## Flyback Output Capacitor

Every balancer flyback output must have a ceramic capacitor on its output. The output capacitor serves as a local, low impedance return path. It also aids during a connection failure, adding charge storage to allow the OVP circuit to detect an open. The capacitor should be sized to allow roughly 10 switch cycles when charging the output from ground to the nominal output voltage, V<sub>OUTPUT,NOM</sub>. Use the following equation to size the output capacitor:

$$C_{FBO} \ge \frac{400 \bullet L_{PRIMARY}}{V_{OUTPUT,NOM}^2}$$

The voltage surge rating must exceed 50•N. The voltage surge rating is usually specified as a multiple of the maximum operating voltage. For capacitor maximum operating voltages less than 100V, the surge rating is

2.5x. For operating voltage between 100V and 630V, the surge rating is typically 1.5x; and for voltages higher than 1000V, the surge rating is 1.2x.

## **Bypass Capacitors**

The LT8584 should be bypassed using 3 capacitors,  $C_{VIN}$ , C<sub>VCELL</sub>, and C<sub>TRAN</sub> (see Block Diagram), using a high-grade (X5R or better) ceramic capacitors. C<sub>VIN</sub> should be placed close to the  $V_{\mbox{\scriptsize IN}}$  pin and should be sized between  $1\mu F$  and  $4.7\mu F.$   $C_{TRAN}$  must be placed close to the transformer's primary winding connection and the IC local ground. The capacitance should range between 47μF and 100μF. Simple mode should have V<sub>SNS</sub>, V<sub>CELL</sub>, and D<sub>CHRG</sub> shorted to V<sub>IN</sub>, which provides an excellent landing for both the transformer primary and a single bypass cap (see the Recommended Layout section). CVIN may be omitted in Simple Mode provided that the C<sub>TRAN</sub> capacitor is in close proximity to the V<sub>IN</sub> pin. C<sub>VCELL</sub> is used for bulk capacitance and should be place close to the battery input connection. Ceramic capacitors are a good choice for bypassing due to their moderate density, low internal series impedance, and very low leakage current. Note that capacitor leakage current at a given operating voltage goes down with increasing capacitor voltage rating. Ceramic capacitors offer the lowest leakage current, while most electrolytic capacitors are quite leaky.

Table 4. Recommended Output Diodes

| MANUFACTURER            | RECOMMENDED TRANSFORMER<br>TURNS RATIO (N) RANGE | PART NUMBER  | I <sub>F(AVG)</sub> (A) | V <sub>RRM</sub><br>(V) | t <sub>rr</sub> (ns) | JUNCTION<br>CAPACITANCE (pF) | PACKAGE |

|-------------------------|--------------------------------------------------|--------------|-------------------------|-------------------------|----------------------|------------------------------|---------|

| STMicroelectronics      | 1 to 2                                           | STPS3H100U   | 3                       | 100                     | N/A                  | 90                           | SMB     |

|                         |                                                  | STPS2H100AY* | 2                       | 100                     | N/A                  | 50                           | SMA     |

|                         | 2 to 4                                           | STTH102AY*   | 1                       | 200                     | 20                   | 12                           | SMA     |

|                         | 10 to 24                                         | STTH112A     | 1                       | 1200                    | 75                   |                              | SMA     |

| Fairchild Semiconductor | 1 to 2                                           | ES2B         | 2                       | 100                     | 20                   | 18                           | SMB     |

| www.fairchildsemi.com   | 2 to 4                                           | ES1D         | 1                       | 200                     | 15                   | 7                            | SMA     |

|                         | 4 to 8                                           | ES1G         | 1                       | 400                     | 35                   | 10                           | SMA     |

|                         | 6 to 12                                          | ES1J         | 1                       | 600                     | 35                   | 8                            | SMA     |

| Vishay                  | 1 to 2                                           | SS2H10*      | 2                       | 100                     | N/A                  | 70                           | SMB     |

| www.vishay.com          |                                                  | U2B          | 2                       | 100                     | 20                   | 16                           | SMB     |

|                         | 2 to 4                                           | ES1D         | 1                       | 200                     | 15                   | 10                           | SMA     |

|                         |                                                  | ES07D-M*     | 1.2                     | 200                     | 25                   | 5                            | SMF     |

|                         | 10 to 20                                         | US1M         | 1                       | 1000                    | 50                   | 10                           | SMA     |

\*AEC-Q101 Qualified

/ LINEAR

## **Discharge Current Sense Resistor**

The discharge current sense resistor,  $R_{SNS}$ , should only be used in serial mode. Omit this resistor and short  $V_{SNS}$  and  $V_{CELL}$  to  $V_{IN}$  in simple mode. The maximum sense voltage between  $V_{VSNS}$  and  $V_{VCELL}$  is 50mV. It is recommended to design for a nominal sense voltage of 30mV. It is not recommended to design for a nominal sense voltage below 20mV since the input offset voltage of the differential amplifier contributes more error at the lower range.

$$R_{SNS} = \frac{V_{VCELL} - V_{VSNS}}{I_{DIS,AV}} = \frac{30mV}{2.5A} = 12m\Omega$$

The internal amplifier amplifies the voltage difference between  $V_{VSNS}$  and  $V_{VCELL}$  20× when  $V_{IN}$  is tied to  $V_{SNS}$ . The voltage is referenced from  $V_{CELL}$  such that:

$$V_{VCELL} - V_{OUT} = 20 \bullet (R_{SNS} \bullet I_{DIS,AV})$$

The measurement is the average discharge current,  $I_{DIS,AV}$ , and not the RMS value. The output,  $V_{VIN}-V_{OUT}$ , is clamped to a maximum of 1V.

## Decode Window Resistor, R<sub>RTMR</sub>

RTMR pin is used to set the duration of the decode window and is programmed by selecting the value of the resistor connected between RTMR and GND. This pin is used in serial mode only. Ground this pin when using simple mode. The decode window is programmable from 1.9ms to 31ms. Set the decode window duration 30% longer than the required time to set the LT8584 in MODE 4 and read back the handshake voltage. This allows the system to detect if there is a communication error. Set  $R_{\rm RTMR}$  based on following equation:

$$R_{RTMR}$$

(k $\Omega$ ) = 0.015 •  $t^2_W$  + 5.9 •  $t_W$  – 1.1

where  $R_{RTMR}$  is given in  $k\Omega$  and  $t_W$  is given in ms.

The RTMR pin is driven to 1.22V approximately 2µs after the part is first enabled. This indicates the decode window is active. The RTMR pin is taken low after the decode window expires. The internal decoder states are latched on the falling edge of RTMR (see Figure 4). The OUT pin multiplexer then selects the correct input corresponding to the programmed mode (refer to Table 1).

#### **OUT Pin Compensation and Filtering**

The OUT pin must have external compensation,  $C_{OUT}$ , for all applications including both serial mode and simple mode. The external capacitor also provides necessary filtering for the input to the BSM. The OUT amplifier is internally compensated to handle capacitance ranging from 20nF to 220nF. Use 47nF for most applications to yield approximately 100µs 1% settling time. A faster amplifier response can be achieved by adding a zero using a resistor in series with the external filter capacitor. Use 4.7nF capacitor with a  $60\Omega$  series resistor to achieve a sub-100us settling time. Note that in serial mode, the capacitors are placed between adjacent LT8584 OUT pins. This effectively doubles the compensation capacitance from the capacitor value used. The OUT amplifier also has internal filtering to both improve PSRR and handle large-signal steps or spikes that may be present on the supply lines.

Additional filtering may be required in noisy environments. Figure 10 shows a two-pole filter with the LT8584 operating in serial mode. The resistors must be kept small to minimize error due to non-zero input currents into the BSM. The LTC6804 is guaranteed to have  $2\mu A$  or less input bias current during measurement. There are two resistors in any given measurement path. Thus, a  $50\Omega$  series resistor will introduce up to a  $200\mu V$  error.  $D_{IN}$  pin current will also cause an error when enabling a particular LT8584, but the error term is canceled when making differential measurements.

Figure 10. Optional OUT Pin Filtering

8584fl

#### HOT SWAP™ PROTECTION

Large currents are developed when hot swapping a battery with a LT8584 application due to the large input bulk capacitance coupled with the low ESR of the batteries. In most cases, the LT8584 should have no problem handling the overshoot voltage that follows the large inrush current. The downstream BSM, however, might encounter damage that requires additional steps and/or circuitry to protect against hot swapping. Several solutions use a two-path method incorporating a pre-charge resistive path and a shunt path (see Figure 11).

Figure 11. Dual Path Hot Swap Solution

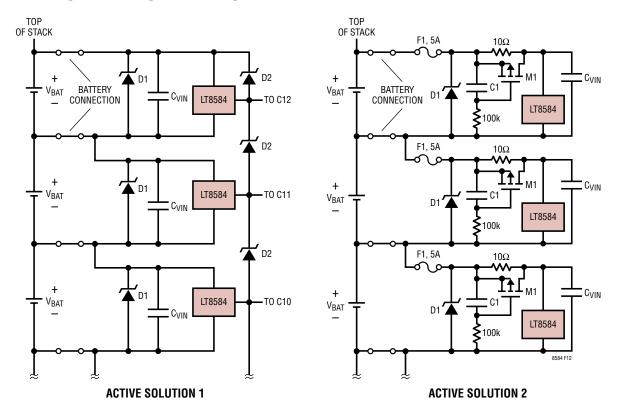

For most applications, use the recommended Hot Swap Solution shown as Active Solution 1 in Figure 12 and in the Typical Application Section. Several other mechanical, active, and order-of-assembly solutions are also given as alternatives or as supplements.

#### **Active Solution**

An active solution has the added advantage of automatic hot swap protection; no additional steps are needed when connecting batteries. Two input protection solutions are shown with the first solution using only TVS diodes. D1 is selected to trigger around 6V and to take the brunt of the connection input pulse. The reverse leakage current is more significant in low-voltage TVS's. Table 5 gives several diodes for D1 that have adequate current and voltage characteristics while minimizing reverse leakage current. D2 provides secondary protection for the BSM inputs. These should be smaller than D1 since the LT8584's OUT pin limits current. Table 6 gives several diodes that are optimal for D2.

The second active solution has additional overvoltage protection via a fuse, F1, and a pre-charge MOSFET circuit.

This method has the disadvantage of lower efficiency and higher cost. Use FETs for M1 in Figure 12 that have low  $R_{DS,ON}$  to maximize converter efficiency and have less than a 1.25V  $V_{GS}$  threshold. Table 7 lists several recommended FETs for M1. C1 should be sized such that C1  $\geq$   $C_{VIN}/500$ .

The third active solution protects the flyback output capacitors. All flyback outputs sum together and flow through D13. During a Hot Swap condition, D13 will reverse bias and prevent a large inrush current into the flyback output capacitors. The peak repetitive reverse voltage,  $V_{RRM}$ , should exceed the maximum module voltage,  $V_{MODULE}$ . Several recommended diodes for D13 are given in Table 8.

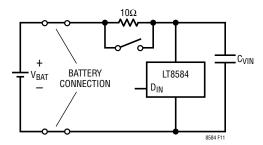

#### **Mechanical Solution**

A mechanical approach may result in a more cost effective solution. A  $10\Omega$  resistor is used to pre-charge the  $C_{VIN}$ capacitor to the battery voltage, limiting the inrush current. After the C<sub>VIN</sub> cap is charged, a mechanical short is connected across the resistor and remains there during all normal operations. There are three recommended solutions for the mechanical short: 1.) use a > 3A rated jumper 2.) use a mechanical switch or 3.) use a staggered-pin battery connector. The staggered pin connection has the long pins connecting to LT8584 through the  $10\Omega$  resistor. The short pins connect directly to the LT8584, shorting out the  $10\Omega$  resistor. Normal insertion has a delay on the order of milliseconds between the long pin connecting and short pin connecting to the circuit, allowing  $C_{VIN}$  to charge up through a current limiting resistor before the mechanical short is made.

## **Order of Assembly**

The order of assembly of the battery stack, the LT8584 balancers, and the BSM can also mitigate hot swapping issues. Having separate boards for both the LT8584 balancers and the BSM is recommended. This allows the LT8584 balancers to be built and connected during the battery stack assembly. The last step involves mating the battery stack and LT8584 assembly with the BSM board. Additional filters on the inputs into the BSM also reduce possible issues during final assembly, see the OUT Pin Compensation and Filtering section for more detail.

**FLYBACK OUTPUT HOT SWAP PROTECTION**

Figure 12. Active Hot Swap Solutions

Table 5. Recommended Transient Voltage Suppressors (TVS) for D1 in Figure 12

| MANUFACTURER       | PART NUMBER   | REVERSE LEAKAGE (μA) | V <sub>P-P</sub> AT I <sub>P-P</sub> | PACKAGE  |

|--------------------|---------------|----------------------|--------------------------------------|----------|

| STMicroelectronics | SM2T6V8A      | 50 at 5V             | 9.2V at 19.6A                        | DO-216AA |

|                    | SM4T6V7AY*    | 20 at 5V             | 9.2V at 43.5A                        | SMA      |

|                    | SMA6T6V7AY*   | 20 at 5V             | 9.1V at 68A                          | SMA      |

| Vishay             | VESD05A1-02V  | 1 at 5V              | 12V at 16A                           | SOD-523  |

|                    | GSOT05*       | 10 at 5V             | 12 at 30A                            | S0T-23   |

| NXP                | PESD5V0S1UA   | 4 at 5V              | 13.5V at 25A                         | SOD-323  |

| Infineon           | ESD5V0S1U-03W | 20 at 5V             | 14V at 40A                           | SOD323   |

<sup>\*</sup>AEC-Q101 Qualified

Table 6. Recommended Transient Voltage Suppressors (TVS) for D2 in Figure 12

| MANUFACTURER       | PART NUMBER   | REVERSE LEAKAGE (μA) | V <sub>P-P</sub> AT I <sub>P-P</sub> | PACKAGE    |

|--------------------|---------------|----------------------|--------------------------------------|------------|

| STMicroelectronics | ESDALC6V1-1M2 | 0.1 at 3V            | 9.2V at 6A                           | S0D882     |

| Vishay             | VBUS051BD-HD1 | 0.1 at 5V            | 16V at 3A                            | LLP1006-2L |

|                    | VESD05-02V    | 0.1 at 5V            | 20V at 6A                            | SOD-523    |

| Diode Inc          | T5V0S5-7      | 0.05 at 5V           | 15V at 5A                            | SOD-523    |

| NXP                | PESD9X5.0L*   | 0.2 at 5V            | 10V at 1A                            | SOD-882    |

<sup>\*</sup>AEC-Q101 Qualified

Table 7. Recommended FETs for M1 in Figure 12

| MANUFACTURER                                  | PART NUMBER | $R_{DS,ON}$ (m $\Omega$ ) AT $V_{GS} = 2.5V$ | I <sub>DS,MAX</sub> (A) | PACKAGE         |

|-----------------------------------------------|-------------|----------------------------------------------|-------------------------|-----------------|

| Fairchild Semiconductor www.fairchildsemi.com | FDS4465     | 10.5                                         | 13.5                    | SO-8            |

|                                               | FDS6576     | 20                                           | 11                      | SO-8            |